32.768kHz晶振电路分析与设计

振荡电路用于实时时钟RTC时,经常使用爱普生FC-135/135R贴片音叉晶振或者C2系列圆柱体晶振(32.768kHz的晶体谐振器)连接在OSC3 与OSC4之间而且为了获得稳定的频率必须外加两个带外部电阻的电容以构成振荡电路。当然,还可以使用内嵌振荡电路的SG7050EAN系列32.768kHz晶体振荡器(有源)。问题是为什么一定要使用32.768kHz这个频率呢?

因为32.768kHz晶振产生的振荡信号经过石英钟内部分频器进行15次分频后得到1Hz秒信号,即秒针每秒中走一下,石英钟内部分频器只能进行15次分频,要是换成别的频率的晶振,15次分频后就不是1Hz的秒信号,钟就不准了。32.768K=32768=2的15次方,数据转换比较方便、精确。因此在很多数字集成电路中都要用到实时时钟(RTC , Real Time Clock) 电路,而确保RTC 工作计时准确的关键部分就是32.756kHz 的晶体振荡电路。

传统的RTC 电路(hth最新网)是采用反相器对晶振产生的波形做整形,所用起振时间需要几个ms ,如果用过多的反相器会加大电路功耗。本文提出一种用晶体起振电路模型和比较器搭建的晶振电路,晶振模型部分用于产生32. 768kHz的正弦波,比较器部分将波形整形为终需要的时钟波形。但是本文中所介绍的整个晶振电路的起振时间只需要几个μs ,而且电路所需静态电流少,耗功率小,版图所占面积也小。整个电路用基于Hsice 做了仿真,验证了电路各参数的准确性及电路的可实现性,并已成功流片并用于基于0. 18μm 工艺下的某系列音频芯片中,为其提供实时时钟。

1 电路结构

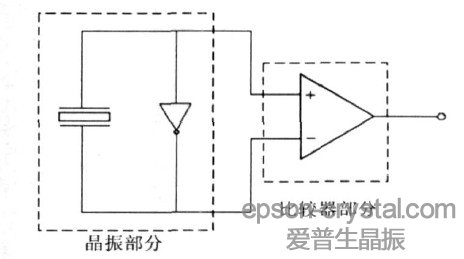

图1 所示为振荡电路结构框架,将晶振模型产生的正弦信号IN 和OUT 作为输入,进入比较器比较后,产生稳定的32k 时钟波形。

图1 晶振的整体电路

2 具体电路分析

按晶振部分和比较器部分分别给出具体电路的分析。

2. 1 晶振部分的电路分析

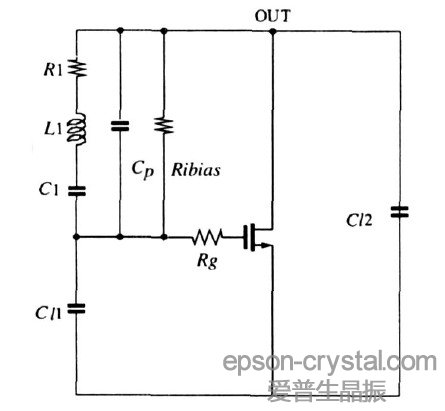

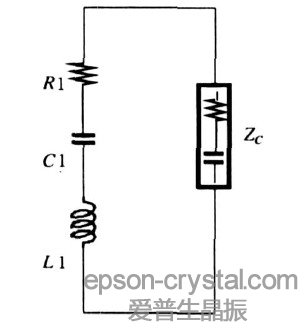

图2 所示是晶振部分所用的具体电路,其中,R1 , C1 ,L1 , Cp 是晶体的等效模型电路。R1 是晶体的等效串联电阻,其值表示晶体的损失,L1 , C1 分别为晶体的等效串联电感和电容,这两个值决定晶体的振荡频率为32. 785kHz ( f = 1P2pi √LC) , Cp 是晶体输入输出引脚间的电容,其值为5 p , Cl1 , Cl2 是晶体的负载电容。图2 中NMOS管M1 作为一个单级反相放大器通过晶振等效电路形成正反馈,从而和栅源( G , S) ,漏源( D , S) 之间的两个负载电容一起形成Pierce 振荡电路的结构。Ribias 和Rg 为NMOS管提供偏置电压。该晶振部分电路在满足巴克豪林准则的条件下可以振荡。

图2 晶振部分的具体电路。

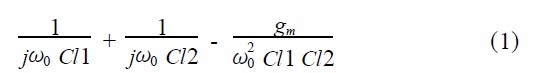

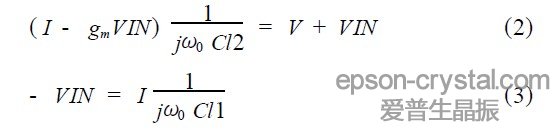

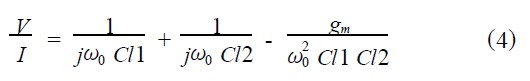

以下通过负阻的角度来分析电路的工作原理,图3 所示为晶振部分等效串联谐振电路,其中NMOS 管M1 和Cl1 , Cl2 的阻抗可以等效为:

其具体等效方法为: 设流进OUT 点的电流为I ,Ribias 两端的电压为V ,NMOS 管上的漏电流为gmVIN ,则:

联立这两个式子,消去VIN 即可得到:

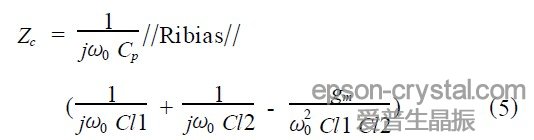

从而,起振电路的等效阻抗:

如果要维持电路振荡,必须保持Zc 的实部与R1 之和是零或者负值,这就对gm 的值提出了要求。

gm 的*小值可以用以下方法估计:

忽略Ribias和Cp ,设定Cl1 = Cl2 = C , Zc 即可简化成:

Zc 实部的值要大于等于R1,所以有:

根据上述条件设定晶振部分电路各器件参数,以满足晶振起振条件后,晶振输入输出端XIN 和XOUT 分别会产生相位相反的正弦信号。

图3 晶振电路的等效电路

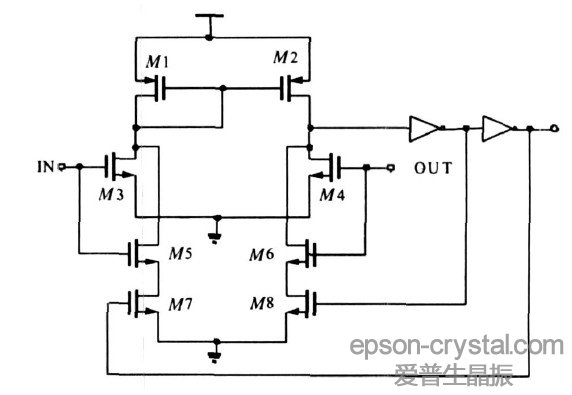

2. 2 比较器部分的电路分析

电路中的比较器电路结构如图4 所示,晶振产生的两个幅度相等相位相反的信号作为输入进入比较器输入。

图4 比较器电路。

M1 - M4 构成伪电流源差分放大器,M5 和M6用来提高输入管M3 和M4 的gm ,M7 和M8 是用输出电压作为其栅极电压,从而控制M3 和M4 的连接与否。当V IN > VOUT时,M3 的漏电流大于M4 上的漏电流,而M1上的电流镜像到M2上,于是M2上的电流大于M4 上的电流,多余的电流将流进反相器1 ,由于反相器的输入电容,电流转化成电压,此时可以认为是数字高电平1 ,那么输出也即为高电平,M7管导通,M5 增加了M3 的gm ,进一步增加反相器1的输入电压,从而使得输出高电平更稳定;反之,当V IN < VOUT时,M3 的漏电流小于M4 上的漏电流,同样M1 上的电流镜像到M2 上,于是M2 上的电流小于M4 上的电流,因此反相器1 的输入电容放电补充这部分电流,此时可以认为反相器1 的输入电压是数字低电平0 ,那么输出也即为低电平,M8 管导通,M6 增加了M4 的gm ,从而将反相器1 的输入电压下拉至更低电平,从而使得输出低电平更稳定。

由于比较器电路的输入电阻趋于无穷大,所用工艺下输入电容数量级为f F , 因此整个电路与晶振电路连接时不会对晶振电路造成影响。

现分析其具体性能如下:

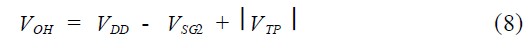

*大输出电压为:

*小输出电压为:

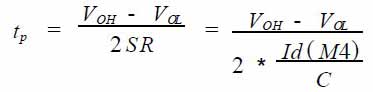

比较器的传输时延为:

其中Id (M4) 是M4 管的漏电流,由于电路采用的伪电流源的结构,所以M4 管的漏电流允许很大,所以使得比较器的传输时延可以很短。

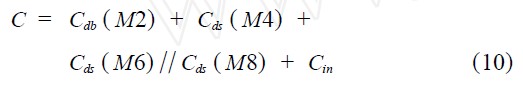

C 是M4 管源端的结点电容,即:

Cin 是反相器的输入电容。

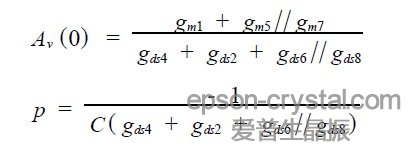

比较器的频率响应可以表示为:

其中

3 电路设计及仿真

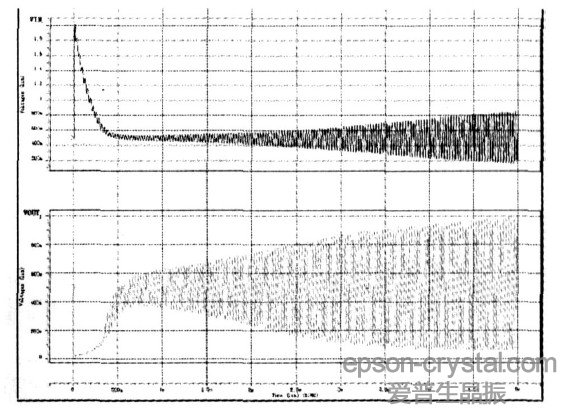

图2 所示电路搭建仿真模型用Hspice 进行仿真。图2 中需要给电路提供一个直流电平,所以在OUT 端连接一个PMOS 管,其源端接电源,漏端和栅端接在OUT 点,作为一个等效电阻。考虑到图1 中NMOS 管的gm 大小的限制,经过计算取WPL =2μP8μ,其gm = 9. 5μs.负载电容Cl1 和Cl2 取10μ,以确保晶振的振荡频率为32. 768kHz , 在实际仿真中可以对负载电容进行调整以获得准确的振荡频率。Ribias 一般取10M 到25M 之间,当Ribias 增大时,NMOS 管的反相放大器的增益增大,此时振荡器的起振时间变小。另外,仿真时为了让电路起振需要在IN 端给一个电流扰动。该部分的仿真结果如图5 所示,IN 和OUT 两端正反馈过程明显,从而产生相位相反的正弦信号。

图5 晶振电路部分IN 和OUT端的电压波形

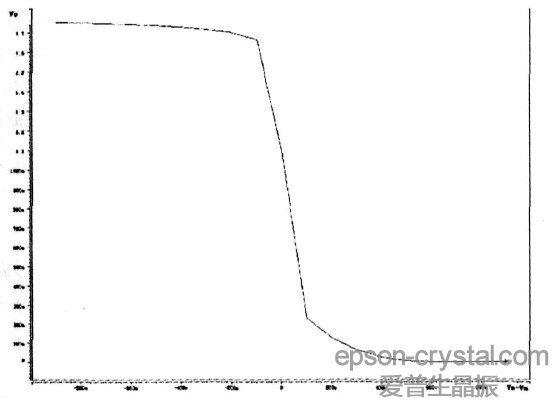

图4 中要求比较器有较高的增益,带宽超过32. 768kHz ,根据给定的输出*大*小值和传输时间设计好各个管子的宽长比后,仿真得到如图6 所示的比较器的传输曲线。

图6 比较器的传输特性曲线。

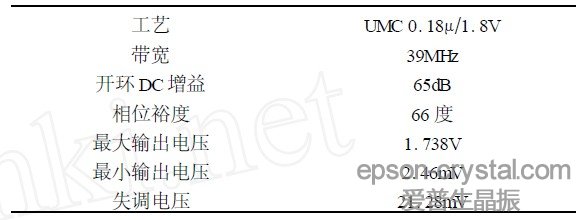

由图6 可测得,VOH = 1. 738V ,VOL = 2. 46mV ,失调电压VOS = 21. 28mV.

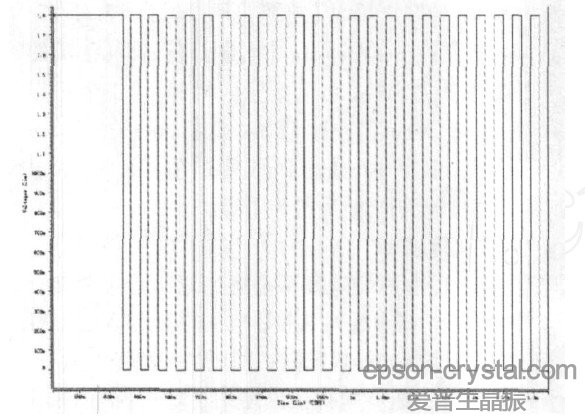

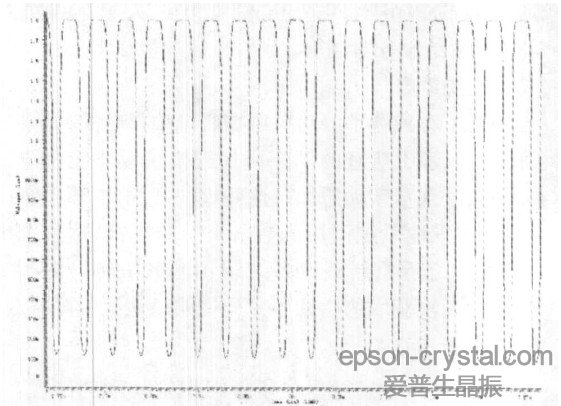

将图2 晶振部分与图4 比较器部分连接后仿真,输出的时钟波形如图7 所示,可以看出其起振时间为625μs ,由于采用的伪电流结构和M5~ M8 的作用,其上升时间仅为0. 017μs , 下降时间仅为0. 008μs.对比用反相器作为整形电路的结构,其起振时间为2ms ,如图8 所示,其终输出的时钟波形也比用比较器结构的差,例如失真度较高,尽管反相器的管子的宽长比很大,波形的上升时间和下降时间也很长,而且它的低电平部分不能完*到达0V.

图7 晶振整体电路的输出时钟波形

图8 用反相器整形后输出时钟波形。

通过仿真可得,该电路的功耗为2. 4292μW.

综上所述,比较器电路的仿真结果如表1 所示,整个晶振电路的仿真结果如表2 所示。

表1 比较器电路仿真结果。

表2 整个振荡电路仿真结果

4 结束语

提出了一种用于实时时钟RTC 的32. 768kHz 集成晶体振荡电路的实现方法,采用晶振和比较器的结构,文中分别给出了这两部分的具体电路和分析,并使用Hspice 对所设计的电路进行仿真,从而验证了该电路起振时间短,波形稳定,功耗低等特点。

-

2020-11-27爱普生TG5032SGN高精度温补晶振替代TG5032SAN说明

-

2020-10-14低抖动差分输出石英晶体振荡器SG7050EBN选购指南

-

2020-10-14RX-8025T设计使用注意事项-爱普生原厂建议

-

2020-10-14哪里有卖贴片晶振fc135 32.7680kaag0与fc135 32.7680k

-

2020-10-14爱普生晶体谐振器&SAW无源晶振停产型号替换说明

-

2020-10-14爱普生温补晶振TCXO停产型号替换官方资料

终端请点

终端请点